Ejercicios Resueltos Arquitectura de Computadores . Parte II

Tema 3

Ejercicio 1

Se tiene la siguiente sentencia en lenguaje C++:

a = b;

Sabiendo que a se almacena en r0 y b en r1, traduce la anterior sentencia al lenguaje CT.

📐Demostración

El código en lenguaje CT sería:

MOV r0, r1

Ejercicio 2

Se tiene la siguiente sentencia en C++:

a = 45;

Sabiendo que a se almacena en r0, traduce la sentencia anterior al lenguaje del CT.

📐Demostración

El código en lenguaje CT sería:

MOVL r0, 45

MOVH r0, 00

En realidad, el MOVH no sería necesario, pero seguro que en el examen lo pondrían mal si no lo pones.

Ejercicio 3

Se tiene la siguiente sentencia en C++:

a = b;

Sabiendo que a se almacena en r0 y b en la dirección de memoria 2010, traduce la sentencia anterior al lenguaje del CT.

📐Demostración

El código en lenguaje CT sería:

MOVH r1, 20h

MOVL r1, 10h

MOV r0, [r1]

Ejercicio 4

Se tiene la siguiente sentencia en C++:

a = b

Sabiendo que a se almacena en la dirección de memoria 3456 y b en r3, traduce la sentencia al lenguaje CT.

📐Demostración

El código en el lenguaje CT sería:

MOVH r0, 34h

MOVL r0, 56h

MOV [r0], r3

Ejercicio 5

Se tiene la siguiente sentencia en C++:

a = b

Sabiendo que a se almacena en la dirección de memoria 3456 y b en la dirección de memoria AB12, traduce la sentencia anterior al lenguaje CT.

📐Demostración

El código en el lenguaje CT sería:

MOVH r0, 34h

MOVL r0, 56h

MOVH r1, ABh

MOVL r1, 12h

MOV r2, [r1]

MOV [r0], r2

Ejercicio 6

Se tiene la siguiente sentencia en C++:

a = b + 5;

Sabiendo que a se almacena en r0 y b en r1, traduce la sentencia anterior al lenguaje CT.

📐Demostración

El código en lenguaje CT sería:

MOVH r2, 0

MOVL r2, 5

ADD r0, r1, r2

Ejercicio 7

Se tiene la siguiente sentencia en C++:

a = b - c

Sabiendo que a se almacena en r0, b en r1 y c en la posición de memoria 4567, traduce la sentencia anterior al lenguaje CT.

📐Demostración

En el lenguaje CT sería:

MOVH r2, 45h

MOVL r2, 67h

MOV r3, [r2]

SUB r0, r1, r3

Ejercicio 8

Se tiene la siguiente sentencia en C++:

a = (b + c) - (a + 1024)

Sabiendo que a se almacena en la dirección de memoria 1000, b en r1 y c en r2, traduce la sentencia anterior al lenguaje CT.

📐Demostración

Primero pasamos 1024 a hexadecimal:

En el lenguaje CT sería:

MOVH r3, 10h

MOVL r3, 00h ; Carga de la dirección de memoria de a

MOV r0, [r3] ; Carga del valor de a

MOVH r4, 04h

MOVL r4, 00h ; Carga de 1024 en hex

ADD r1, r1, r2 ; (b + c)

ADD r0, r0, r4 ; (a + 1024)

SUB r0, r1, r0 ; (b + c) - (a + 1024)

MOV [r3], r0 ; Guardamos el resultado en memoria

Ejercicio 9

Se tiene la siguiente sentencia en C++:

if (a == b)

c = c + 1;

Sabiendo que a se almacena en r0, b en r1 y c en r2, traduce la sentencia anterior al lenguaje CT.

📐Demostración

En el lenguaje CT sería:

CMP r0, r1 ; Comparamos a y b haciendo la resta a - b

BRZ consecuente ; Si ZF = 1 --> a = b --> saltamos a consecuente

JPM siguiente ; Si no saltamos a siguiente

consecuente:

MOVL r3, 1

MOVH r3, 0

ADD r2, r2, r3

siguiente:

Ejercicio 10

Se tienen las siguientes sentencias en C++:

if (a != b)

c = c - a;

Sabiendo que a se almacena en r0, b en r1 y c en txr2, traduce la sentencia anterior al lenguaje CT.

📐Demostración

En el lenguaje CT sería:

CMP r0, r1 ; Comparamos a y b haciendo la resta a - b

BRNZ consecuente ; Si ZF = 0 --> a != b --> saltamos a consecuente

JPM siguiente

consecuente:

SUB r2, r2, r0

siguiente:

Ejercicio 11

Se tienen las siguientes sentencias en C++:

if (a < b)

c = 0;

Sabiendo que a se almacena en r0, b en r1 y c en r2, realiza la traducción al lenguaje del CT. Las variables a, b y c almacenan números naturales

📐Demostración

En el lenguaje CT sería:

CMP r0, r1 ; Resta a - b

BRC consecuente ; Si CF = 1 --> a < b ya que hay acarreo

JPM siguiente

consecuente:

XOR r2, r2, r2 ; c = 0

siguiente:

Notar que cuando hacemos la resta de dos números naturales, si el sustraendo es mayor que el minuendo entonces, en la ALU, el bit de acarreo (CF) se pone a 1.

Ejercicio 12

Se tienen las siguientes sentencias en C++:

if (a <= b)

c = 27;

Sabiendo que a se almacena en r0, b en r1 y c en r2, realiza la traducción al lenguaje del CT. Las variables a, b y c almacenan números naturales.

📐Demostración

El código en lenguaje CT sería:

CMP r0, r1

BRC consecuente ; Si CF = 1 --> a < b

BRZ consecuente ; Si ZF = 1 --> a = b

JPM siguiente

consecuente:

MOVL r2, 27

MOVH r2, 0

siguiente:

Ejercicio 13

Se tienen las siguientes sentencias en C++:

if ((a == b) && (a != c))

a = 0;

Sabiendo que a se almacena en r0, b en r1 y c en r2, realiza la traducción al lenguaje del CT. Las variables a, b y c almacenan números naturales.

📐Demostración

El código en lenguaje CT sería:

CMP r0, r1

BRNZ siguiente ; Si ZF = 0 --> a != b

CMP r0, r2

BRZ siguiente ; Si ZF = 1 --> a = c

XOR r0, r0, r0 ; a = 0

siguiente:

Notar que en este caso, se han empleado las leyes de De Morgan, es decir:

Alternativamente, se podría haber hecho:

CMP r0, r1

BRZ segunda_comprobacion ; Si ZF = 1 --> a = b

JMP siguiente

segunda_comprobacion:

CMP r0, r2

BRNZ consecuente ; Si ZF = 0 --> a != c

JMP siguiente

consecuente:

XOR r0, r0, r0 ; a = 0

siguiente:

Ejercicio 14

Se tienen las siguientes sentencias en C++:

if ((a == b) || (a != c))

a = 0;

Sabiendo que a se almacena en r0, b en r1 y c en r2, realiza la traducción al lenguaje del CT. Las variables a, b y c almacenan números naturales.

📐Demostración

El código en lenguaje CT sería:

CMP r0, r1

BRZ consecuente ; Si ZF = 1 --> a = b

CMP r0, r2

BRNZ consecuente ; Si ZF = 0 --> a != c

JMP siguiente

consecuente:

XOR r0, r0, r0 ; a = 0

siguiente:

Ejercicio 15

Se tienen las siguientes sentencias en C++:

for (i = 0; i < 100; i++)

a = a - i;

Sabiendo que a se almacena en r5, i en r0 y es natural, realiza la traducción al lenguaje del CT.

📐Demostración

El código en lenguaje CT sería:

XOR r0, r0, r0 ; i = 0

MOVH r1, 0

MOVL r1, 100 ; Cargamos 100 en r1

inicio_for:

CMP r0, r1

BRNC fin_for ; Si CF = 0 --> i >= 100

SUB r5, r5, r0 ; a = a - i

INC r0 ; i++

JMP inicio_for

fin_for:

Ejercicio 16

Se tienen las siguientes sentencias en C++:

i = 0;

while (i < 100){

a = a - i;

i++;

}

Sabiendo que a se almacena en r5 e i en r0 y es natural, realiza la traducción al lenguaje del CT.

📐Demostración

El código en lenguaje CT sería:

XOR r0, r0, r0 ; i = 0

MOVL r1, 100

MOVH r1, 0 ; Cargamos 100 en r1

inicio_while:

CMP r0, r1

BRNC fin_while ; Si CF = 0 --> i >= 100

SUB r5, r5, r0 ; a = a - i

INC r0 ; i++

JMP inicio_while

fin_while:

Ejercicio 17

Se tienen las siguientes sentencias en C++:

i = 0;

do {

a = a - i;

i++;

} while (i < 100);

Sabiendo que a se almacena en r5 e i en r0 y es natural, realiza la traducción al lenguaje del CT.

📐Demostración

El código en lenguaje CT sería:

XOR r0, r0, r0 ; i = 0

MOVL r1, 100

MOVH r1, 0 ; Cargamos 100 en r1

inicio_do_while:

SUB r5, r5, r0 ; a = a - i

INC r0 ; i++

CMP r0, r1

BRC inicio_do_while ; Si CF = 1 --> i < 100

Ejercicio 18

Se tienen las siguientes sentencias en C++:

x = Min(a, b);

Sabiendo que a se almacena en r4, b se almacena en r5, x en r6, el paso de parámetros se realiza a través de los registros r1 y r2 para el primer y segundo parámetro respectivamente y que el valor de retorno se almacena en r0, realiza la traducción al lenguaje del CT.

📐Demostración

El código en lenguaje CT sería:

MOV r1, r4 ; Pasamos el primer parámetro

MOV r2, r5 ; Pasamos el segundo parámetro

CALL Min ; Llamamos a la función Min

MOV r6, r0 ; Guardamos el valor de retorno en x

Ejercicio 19

Se tiene la siguiente sentencia en C++:

x = Min(a, b);

Sabiendo que a se almacena en r4, b en r5, x en r6, el paso de parámetros se realiza a través de la pila de derecha a izquierda por valor y que el valor de retorno se almacena en r0, realiza la traducción al lenguaje del CT.

📐Demostración

El código en lenguaje CT sería:

PUSH r5 ; Pasamos el segundo parámetro

PUSH r4 ; Pasamos el primer parámetro

CALL Min ;

INC r7

INC r7 ; Ajustamos el puntero de pila

MOV r6, r0 ; Guardamos el valor de retorno en x

Ejercicio 20

Se tienen las siguientes sentencias en C++:

int Min (unsigned int a, unsigned int b){

if (a < b)

return a;

else

return b;

}

Sabiendo que a y b se han pasado como parámetros a través de los registros r1 y r2 respectivamente y que el valor de retorno se almacena en r0, realiza la traducción al lenguaje del CT.

📐Demostración

El código en lenguaje CT sería:

Min:

CMP r1, r2

BRNC consecuente:

MOV r0, r2

JMP siguiente

consecuente:

MOV r0, r1

siguiente:

RET

Ejercicio 21

Se tienen las siguientes sentencias en C++:

int Min (unsigned int a, unsigned int b){

if (a < b)

return a;

else

return b;

}

Sabiendo que a y b se han pasado como parámetros a través de la pila de derecha a izquierda y que el valor de retorno se almacena en r0, realiza la traducción al lenguaje del CT.

📐Demostración

El código en lenguaje CT sería:

Min:

PUSH r6 ; Guardamos el valor de r6

MOV r6, r7 ; Guardamos el puntero de pila en r6

PUSH r1 ; Guardamos lo que hay en r1

PUSH r2 ; Guardamos lo que hay en r2

INC r6

INC r6 ; Ajustamos el puntero de pila para los parámetros

MOV r1, [r6] ; Cargamos el primer parámetro -> a

INC r6 ; Ajustamos el puntero de pila para el segundo parámetro

MOV r2, [r6] ; Cargamos el segundo parámetro -> b

CMP r1, r2

BRC consecuente: ; Si CF = 1 --> a < b

MOV r0, r2 ; Retornamos b

JMP siguiente

consecuente:

MOV r0, r1 ; Retornamos a

siguiente:

POP r2 ; Recuperamos lo que había en r2

POP r1 ; Recuperamos lo que había en r1

POP r6 ; Recuperamos el valor de r6

RET

Ejercicio 22

Se tiene la siguiente sentencia en C++:

Min(x, a, b);

Sabiendo que a se almacena en r4, b}se almacena en r5, x en la dirección de memoria 1000, el paso de parámetros se realiza a través de la pila de derecha a izquierda, x se pasa por dirección y los otros dos parámetros por valor y que el valor de retorno se almacena en r0, realiza la traducción al lenguaje del CT.

📐Demostración

El código en lenguaje CT sería:

PUSH r5 ; Pasamos b

PUSH r4 ; Pasamos a

MOVL r0, 0

MOVH r0, 10h

PUSH r0 ; Pasamos la dirección de memoria de x

CALL Min

INC r7

INC r7

INC r7 ; Ajustamos el puntero de pila

Ejercicio 23

Se tiene la siguiente sentencia en C++:

void Min (unsigned int& x, unsigned int a, unsigned int b){

if (a < b)

x = a;

else

x = b;

}

Sabiendo que x, a y b se han pasado como parámetros a través de l pila de derecha a izquierda, realiza la traducción al lenguaje del CT.

📐Demostración

La traducción al lenguaje CT sería:

Min:

PUSH r6

MOV r6, r7

PUSH r1

PUSH r2

PUSH r3 ; Salvaguardamos los valores que hay en r1, r2 y r3

INC r6

INC r6 ; Ajustamos el puntero de pila para los parámetros

MOV r1, [r6] ; Cargamos el primer parámetro -> x

INC r6 ; Ajustamos el puntero de pila para a

MOV r2, [r6] ; Cargamos el segundo parámetro -> a

INC r6 ; Ajustamos el puntero de pila para b

MOV r3, [r6] ; Cargamos el tercer parámetro -> b

CMP r2, r3

BRC consecuente ; Si CF = 1 --> a < b

MOV [r1], r3 ; x = b (x no es local)

JMP siguiente

consecuente:

MOV [r1], r2 ; x = a

siguiente:

POP r3

POP r2

POP r1

POP r6 ; Recuperamos los valores de r1, r2, r3 y r6

RET

Ejercicio 24

Se tiene la siguiente sentencia en C++:

int SumaAcumulada(int Vector[], unsigned int NumElems){

int Suma;

unsigned int i;

Suma = 0;

for (i = 0; i < NumElems; i++)

Suma = Suma + Vector[i];

return Suma;

}

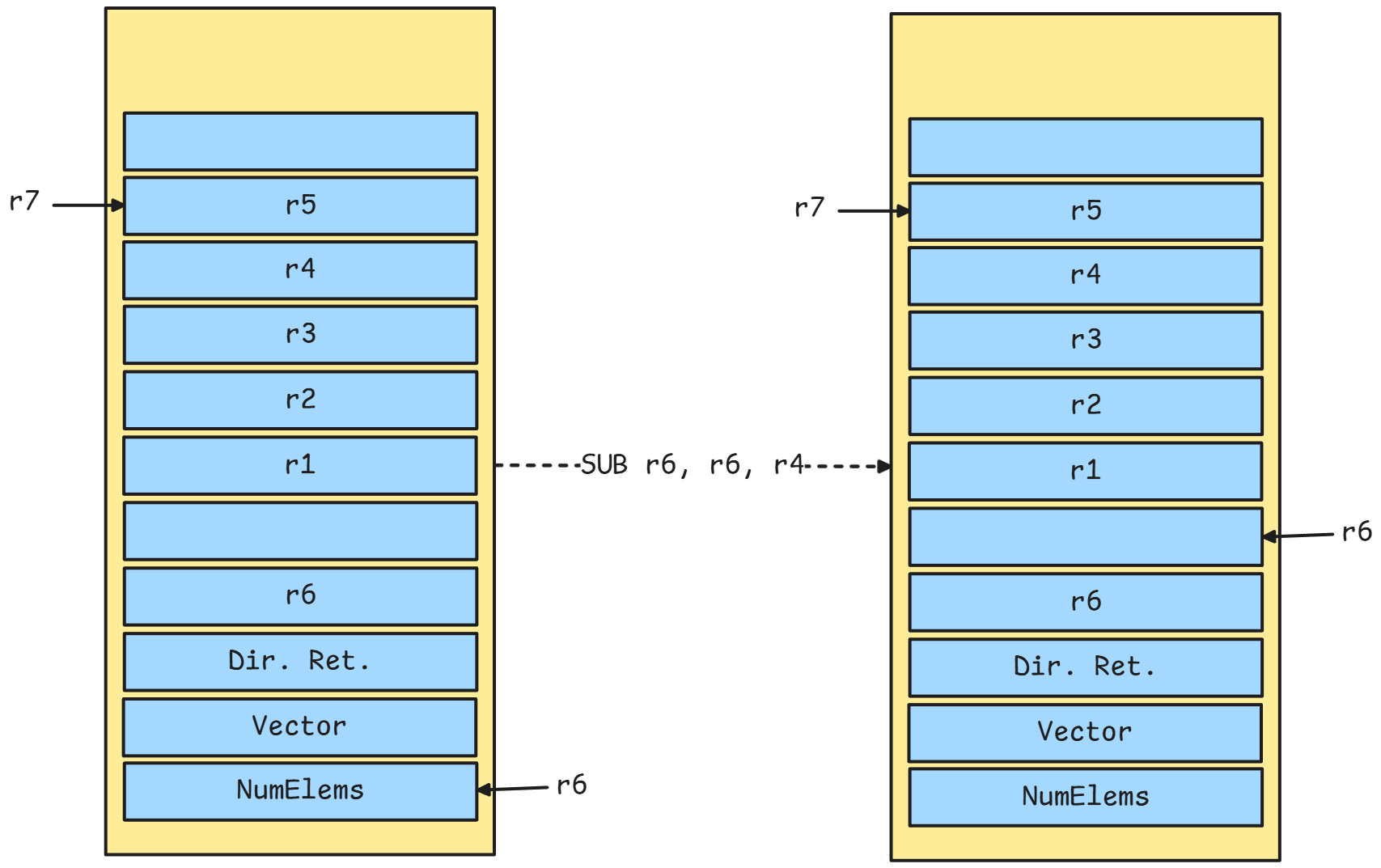

Sabiendo que Vector y NumElemns se han pasado como parámetros a través de la pila de derecha a izquierda, que el valor de retorno se almacena en r0, que la variable local Suma se almacena en la pila y la variable local i en r3, realiza la traducción al lenguaje del CT.

📐Demostración

El código en lenguaje CT sería:

SumaAcumulada:

PUSH r6

MOV r6, r7 ; Prólogo

DEC r7 ; Reservamos espacio para variable Suma

PUSH r1

PUSH r2

PUSH r3

PUSH r4

PUSH r5 ; Salvaguardamos los valores de r1, r2, r3, r4 y r5

INC r6

INC r6

MOV r1, [r6] ; Cargamos el primer parámetro -> Vector

INC r6

MOV r2, [r6] ; Cargamos el segundo parámetro -> NumElems

MOVL r4, 4

MOVH r4, 0

SUB r6, r6, r4 ; r6 = &Suma (ver *)

XOR r4, r4, r4

MOV [r6], r4 ; Suma = 0

XOR r3, r3, r3 ; i = 0

inicio_for:

CMP r3, r2

BRNC fin_for ; Si CF = 0 --> i >= NumElems

ADD r5, r1, r3 ; dirección de la posición i-ésima de Vector

MOV r5, [r5] ; r5 = Vector[i]

MOV r4, [r6] ; r4 = Suma

ADD r4, r4, r5 ; Suma = Suma + Vector[i]

MOV [r6], r4 ; Guardamos el valor de Suma en la pila

INC r3 ; i++

JMP inicio_for

fin_for:

MOV r0, [r6] ; r0 = Suma

POP r5

POP r4

POP r3

POP r2

POP r1

INC r7

POP r6

RET

(*) Cargamos un 4 en r4 para que, al restarle 4 a r6, apuntemos a la dirección de memoria de Suma ya que hemos incrementado 3 veces r6 y el espacio de la variable Suma está uno por encima. Basta notar que:

Tema 5

Ejercicio 1

Codificar la siguientes instrucciones:

MOV r1, r0

📐Demostración

Para codificar la instrucción vemos que:

- El

MOVes un direccionamiento a registro, es decir

- La codificación de la orden

MOVes:

- Como

r0es000yr1es001, la codificación de la instrucción sería:

- Podemos pasar a hexadecimal:

MOV r1, [r0]

📐Demostración

Ahora iremos directamente:

MOV [r0], r1

📐Demostración

La codificación de la instrucción sería:

MOVH r1, 27h

📐Demostración

La codificación de la instrucción sería:

SUB r0, r1, r2

📐Demostración

La codificación será:

CMP r0, r1

📐Demostración

La codificación será:

DEC r1

📐Demostración

La codificación será:

JMP -2

📐Demostración

La codificación será:

Notar que:

BRNO 80h

📐Demostración

La codificación sería la siguiente:

Ejercicio 2

Se considera el siguiente fragmento de código

XOR r1, r1, r1

MOVL r2, 15

MOVH r2, 0

bucle:

MOV r5, [r0]

CMP r2, r5

BRNZ seguir

INC r1

seguir:

INC r0

DEC r6

BRNZ bucle

¿Cuál es la codificación de la instrucción BRNZ seguir? ¿Y la de BRNZ bucle?

📐Demostración

Para la codificación de BRNZ seguir tenemos que saltar a seguir que está a 1 instrucción de distancia, por lo que la codificación sería:

Y para BRNZ bucle tenemos que saltar a bucle que está 7 instrucciones hacia atrás, es decir, -7:

Entonces la codificación será:

Ejercicio 3

El siguiente fragmento de código está cargado en la dirección 500 de la memoria de un computador teórico:

MOV r1, [r0]

INC r0

bucle:

MOV r2, r1

MOV r1, [r0]

CMP r2, r1

BRZ seguir

INC r0

JMP bucle

seguir:

¿Qué valor hay en la dirección 505? ¿Y en la 507?

📐Demostración

Como empieza en la 500, entonces en esta estará la codificación de MOV r1, [r0]. Así, podemos seguir avanzando y tenemos que la siguiente será INC r0, luego MOV r2, r1, luego MOV r1, [r0] y luego CMP r2, r1. Por lo tanto, en la dirección 505 estará la codificación de BRZ seguir.

Para hallar ahora su codificación, tenemos que seguir está a 2 instrucciones de distancia, por lo que la codificación será:

Por último, en la dirección 507 estará la codificación de JMP bucle. Como bucle está a -6 instrucciones de distancia:

Y la codificación será:

Ejercicio 4

Se quiere añadir una nueva instrucción al juego de instrucciones del COmputador Teórico. Se trata de la instrucción CMP [Ri], Inm8 que compara el contenido de la posición de memoria apuntada por el registro Ri con un valor inmediato de 8 bits. Escribir, en el menor número de pasos posible, las señales que debería generar la unidad de control para ejecutar la instrucción CMP [r0], 25 a partir del cuarto paso.

📐Demostración

La idea es hacer la resta de los dos valores en la ALU, para ello, vamos a pasar primero el valor de r0 al MAR para seleccionar la dirección que queremos leer, así empleamos

Ahora hay que hacer un ciclo de espera para que se cargue el dato en el MDR, por lo que no hacemos nada.

Ya tenemos el dato que estaba almacenado en la posición de memoria a la que apuntaba r0 en el MDR, así, vamos a leerlo y pasarselo al registro temporal de la ALU, es decir:

Ahora, vamos a cargar el segundo valor, es decir, el Inm8 haciendo una extensión de signo en el IB para hacer la resta en la ALU y ver el resultado de los bits de estado. Así, empleamos:

Y ya hemos terminado ya que hemos hecho la comparación de los dos valores.

Ejercicio 5

Si en un momento determinado el valor de SR es C=0, O=0, Z=1, N=0, ¿qué señales de control se generan en el paso T4 de la instrucción BRNZ?

📐Demostración

Como tenemos que Z = 1 y queremos ver con BRNZ si Z = 0, entonces no se cumple la condición y no se salta, por lo que las señales de control serán:

Ejercicio 6

Sabiendo que el registro TMPE del computador teório contienen el valor AB65 y que el bus interno contiene el valor 72CC, ¿qué valor habrá en el TMPS y en los flags ZCOS del SR tras la activación de las señales de control SUB, ALU-TMPS y ALU-SR?. Responder en hexadecimal.

📐Demostración

Si en el registro temporal tenemos el valor AB65 y en el IB el valor 72CC y hacemos la resta (SUB) tenemos que:

Así, hacemos para la resta el complemento a 2 del segundo valor:

Así, el valor resultante que se almacena en TMPS es:

Y para los flags, tenemos que:

- El resultado no es cero, entonces

Z = 0 - El sustraendo (interpretado como natural) es menor que el minuendo, entonces

C = 0 - El resultado tiene overflow, entonces

O = 1 - El resultado como entero es positivo, entonces

S = 0

Así, tenemos que:

Ejercicio 7

Se quiere implementar una nueva instrucción en el computador teórico que apile un valor inmediato de 8 bits extendiendo el signo a 16. El mnemónico de la instrucción que se quiere implementar será: PUSH Inm8. El dato inmediato irá codificado en el byte de menor peso.

Indicar la secuencia de pasos de control (pasos 4 y posteriores) necesarios para ejecutar dicha instrucción. No se debe añadir ninguna señal de control en el paso 4 y 5.

📐Demostración

Lo primero será será cargar el valor inmediato en el IB extendido de signo y pasarlo al MDR para luego apilarlo. Así, tenemos:

Ahora, tenemos que pasar la dirección de memoria que apunta a la cima de la pila al MAR pero decrementando una unidad para que apunte a la siguiente dirección de memoria. Así, empleamos:

Y finalmente se lo pasamos al MAR y le decimos que escriba en la dirección de memoria que apunta el MAR el valor que hay en el MDR:

Esperamos un ciclo para que se escriba y finalizamos.

Ejercicio 8

Se quiere añadir una nueva instrucción al juego de instrucciones del CT. Se trata de una instrucción aritmética DUP Rd/s que, como su propio mnemónico indica, duplica el contenido del registro Rd/s. Escribir en el menor número de pasos posible, las señales que debería de generar la unidad de contro para ejecutar DUP r0.

📐Demostración

Primero hay que realizar las tres instrucciones comunes a todos las instrucciones (ver en teoría las epxlicaciones):

Podemos hacer la operación sumando dos veces el valor almacenado en el registro r0. Además, como vamos a sacar el registro al IB para meterlo al TMPE podemos hacer la suma directamente (ya que tenemos tanto en el TMPE como en el IB el valor de r0). Así, empleamos:

Ahora, pasamos el valor del TMPS al IB para poder escribirlo en el registro r0:

Ejercicio 9

En un ciclo determinado aparece en IR el valor 13C0. ¿Qué señales de control se activarán en los ciclos posteriores?

📐Demostración

Lo primero que hay que hacer es decodificar la instrucción que aparece en el IR. Así, tenemos que:

Así, una vez se ha cargado esto en el IR, las señales de control que se generarán son las siguientes

Primero, hay que conseguir el valor que está en la dirección a la que apunta r6 para ello:

Ahora, hay un ciclo de espera ya que no podemos hacer nada hasta que no llegue el dato al MDR.

Una vez que ha llegado, tenemos que pasarlo al registro r3, para ello:

Ejercicio 10

Durante la ejecución de un programa paso a paso en el CR se han observado los valores de algunos registros. Dichos valores se muestran en la siguiente tabla.

Durante los pasos anteriores se ha ejecutado el final de una instrucción A, una instrucción completa B y el principio de una instrucción C. Cuál es la codificación de la instrucción B? Responde en hexadecimal.

📐Demostración

Como en la iteración estábamos en la instrucción A y vemos que en las siguientes dos iteraciones llegamos a que PC = 0410, entonces vemos que se ha sumado uno al PC, es decir, que estamos actualizando el valor de PC por ser el inicio de una nueva instrucción. En este caso, la instrucción B empezará en k + 1. Podemos ver que dura hasta k + 8 (incluido) ya que en k + 10 se actualiza el valor de PC incrementando uno, que es el paso 2 de las instrucciones comunes para cada instrucción, por lo que C se empezó a desarrllar en .

Veamos que hace la instrucción B. Los pasos son los tres pasos generales que se hacen para cada instrucción. Podemos ver que en la instrucción k + 8 el PC pasa a 0400 por lo que podemos suponer que la instrucción modifica este valor, por lo que puede ser un salto JMP o una llamada a una subrutina CALL. Como se ha modificado también el valor de r7, podemos ver que se ha apilado algo en la pila, es decir, que se ha llamado a una subrutina y se ha apilado la dirección de retorno. Por ello, lo que tenemos una instrucción CALL que salta a la dirección 0400.

Así, como estábamos en 0410 y hemos saltado a 0400, tenemos que la instrucción B es un CALL a la dirección 0400 que está 16 posiciones por detrás. Por lo que la codificación de la instrucción será:

Ejercicio 11

En un paso de ejecución del computador teórico, el valor del TMPE es ACDF, el valor del r0 es 7FB3 y se encuentran activadas las siguientes señales de control:

¿Cuál será el valor del TMPS y del SR (ZCOS) al final del paso? Responder en Hex

📐Demostración

Como tenemos que en el TMPE está el valor ACDF y en el r0 el valor 7FB3 y se está mandando al IB con el R0-IB. Dado que en la ALU hay un XOR entonces decodificamos ambos valores y tenemos que:

Así, hacemos la operación:

Por lo que el resultado en hexadecimal será:

Y el valor de los flags será:

Z= 0 ya que el resultado no es ceroC= 1 ya que el la suma de bits más significativos genera carryO= 0 ya que no hay overflowS= 1 ya que el resultado es negativo

Por lo que el valor de los flags será:

Ejercicio 12

En un determinado paso de ejecución de una instrucción correspondiente al juego de instrucciones del computador teórico, el valor del registros r4 es igual a 5678, el valor del registro TMPE es 1234 y se encuentran activadas las señales de control R4-IB, ALU-TMPS, SUB, ALU-SR. ¿Qué valor contendrán el registro TMPS y el registro de estado ZCOS al finalizar dicho paso de ejecución?. Responder en hexadecimal.

📐Demostración

Vamos a decodificar los valores que tenemos:

Por lo que, para hacer la resta hacemos el complemento a 2 del sustraendo:

Y ahora hacemos la suma:

Así, el restultado que aparecerá en el TMPS es:

Y los bits de estado serán:

Z= 0 ya que el resultado no es ceroC= 1 ya que interpretando la resta como naturales el sustraendo es mayor que el minuendoO= 0 ya que no hay overflowS= 1 ya que el resultado es negativo

Por lo que el valor de los flags será:

Ejercicio 13

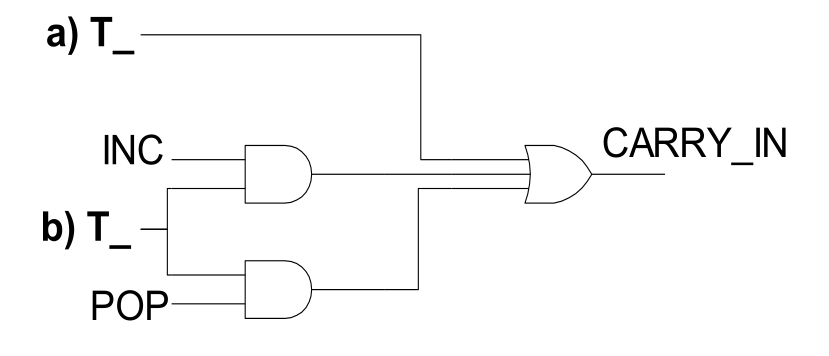

El circuito de la figura muestra una parte del circuito generador de señales de una unidad de control cableada para la CPU teórica. La parte mostrada está orientada a la generación de señal CARRY\_IN

¿Cuáles son las señales generadas por el contador de pasos necesarias en a) y b) (Señales T\_n donde N es el número de paso en el bloque que se activaría esa línea)